#### LPM9435

## P-Channel Enhancement Mode Field Effect Transistor

## **General Description**

The LPM9435 is the P-channel logic enhancement mode power field effect transistors are produced using high cell density, DMOS trench technology. This high density process is especially tailored to minimize on-state resistance.

These devices are particularly suited for low voltage application, notebook computer power management and other battery powered circuits where high=-side switching.

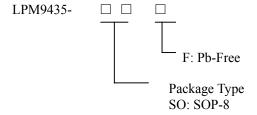

## **Ordering Information**

#### **Features**

- -30V/-5.8A,RDC(ON)= $38m\Omega(typ.)$ @VGS=-10V

- -30V/-4.0A,RDC(ON)= $60m\Omega(typ.)$ @VGS=-4.5V

- Super high density cell design for extremely low RDC(ON)

- SOP8 Package

## **Applications**

- ♦ Portable Media Players

- ♦ Cellular and Smart mobile phone

- ♦ LCD

- ♦ DSC Sensor

- ♦ Wireless Card

# **Marking Information**

Please see website.

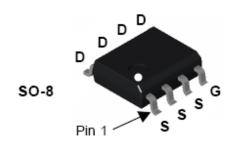

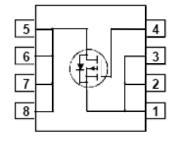

## **Pin Configurations**

SOP8(Top View)

# **Functional Pin Description**

# Absolute Maximum Ratings T<sub>A</sub>=25°C unless otherwise noted

| Symbol                            | Parameter                                        |           | Ratings     | Units |

|-----------------------------------|--------------------------------------------------|-----------|-------------|-------|

| V <sub>DSS</sub>                  | Drain-Source Voltage                             |           | -30         | V     |

| V <sub>GSS</sub>                  | Gate-Source Voltage                              |           | ±25         | V     |

| Ь                                 | Drain Current - Continuous                       | (Note 1a) | -5.3        | A     |

|                                   | - Pulsed                                         |           | -50         |       |

| P₀                                | Power Dissipation for Single Operation           | (Note 1a) | 2.5         | W     |

|                                   |                                                  | (Note 1b) | 1.2         |       |

|                                   |                                                  | (Note 1c) | 1           |       |

| T <sub>J</sub> , T <sub>STG</sub> | Operating and Storage Junction Temperature Range |           | -55 to +175 | °C    |

| Therma                            | l Characteristics                                | •         |             | •     |

| R <sub>eja</sub>                  | Thermal Resistance, Junction-to-Ambient          | (Note 1a) | 50          | °C/W  |

| R <sub>eJA</sub>                  | Thermal Resistance, Junction-to-Ambient          | (Note 1c) | 125         | °C/W  |

| Rejc                              | Thermal Resistance, Junction-to-Case             | (Note 1)  | 25          | °C/W  |

|                                   |                                                  |           |             |       |

| Symbol                           | Parameter                                         | Test Conditions                                                           | Min | Тур  | Max  | Units |

|----------------------------------|---------------------------------------------------|---------------------------------------------------------------------------|-----|------|------|-------|

| Off Char                         | acteristics                                       |                                                                           |     | 1    | 1    |       |

| BV <sub>DSS</sub>                | Drain-Source Breakdown Voltage                    | $V_{GS} = 0 \text{ V}, I_D = -250 \mu\text{A}$                            | -30 |      |      | V     |

| <u>ΔBVpss</u><br>ΔT <sub>J</sub> | Breakdown Voltage Temperature<br>Coefficient      | l₀ = −250 μA, Referenced to 25°C                                          |     | -23  |      | mV/°C |

| DSS                              | Zero Gate Voltage Drain Current                   | V <sub>DS</sub> = -24 V, V <sub>GS</sub> = 0 V                            |     |      | -1   | μΑ    |

| GSSF                             | Gate–Body Leakage, Forward                        | $V_{GS} = 25 \text{ V},  V_{DS} = 0 \text{ V}$                            |     |      | 100  | nΑ    |

| GSSR                             | Gate–Body Leakage, Reverse                        | $V_{GS} = -25 \text{ V}$ $V_{DS} = 0 \text{ V}$                           |     |      | -100 | nA    |

| On Char                          | acteristics (Note 2)                              |                                                                           |     |      |      |       |

| $V_{GS(th)}$                     | Gate Threshold Voltage                            | $V_{DS} = V_{GS}, I_{D} = -250 \mu A$                                     | -1  | -1.7 | -3   | V     |

| ΔV gs(th)<br>ΔTJ                 | Gate Threshold Voltage<br>Temperature Coefficient | $I_D$ = -250 μA, Referenced to 25°C                                       |     | 4.5  |      | mV/°C |

| R <sub>DS(on)</sub>              | Static Drain-Source                               | $V_{GS} = -10 \text{ V},  I_D = -5.3 \text{ A}$                           |     | 42   | 50   | mΩ    |

|                                  | On–Resistance                                     | $V_{GS} = -4.5 \text{ V},  I_D = -4 \text{ A}$                            |     | 65   | 80   |       |

|                                  |                                                   | $V_{GS} = -10 \text{ V}, I_D = -5.3 \text{ A}, T_J = 125^{\circ}\text{C}$ |     | 57   | 77   |       |

| I <sub>D(on)</sub>               | On-State Drain Current                            | $V_{GS} = -10 \text{ V}, \qquad V_{DS} = -5 \text{ V}$                    | -25 |      |      | Α     |

| g <sub>FS</sub>                  | Forward Transconductance                          | $V_{DS} = -5 \text{ V}, \qquad I_{D} = -5.3 \text{ A}$                    |     | 10   |      | S     |

| Dynamic                          | Characteristics                                   |                                                                           |     |      |      |       |

| Ciss                             | Input Capacitance                                 | $V_{DS} = -15 \text{ V},  V_{GS} = 0 \text{ V},$                          |     | 528  |      | pF    |

| Coss                             | Output Capacitance                                | f = 1.0 MHz                                                               |     | 132  |      | pF    |

| Crss                             | Reverse Transfer Capacitance                      |                                                                           |     | 70   |      | pF    |

| Switchin                         | g Characteristics (Note 2)                        |                                                                           |     | •    | •    | •     |

| t <sub>d(on)</sub>               | Turn-On Delay Time                                | $V_{DD} = -15 \text{ V},  I_D = -1 \text{ A},$                            |     | 7    | 14   | ns    |

| t <sub>r</sub>                   | Turn-On Rise Time                                 | $V_{GS} = -10 \text{ V}, \qquad R_{GEN} = 6 \Omega$                       |     | 13   | 24   | ns    |

| t <sub>d(off)</sub>              | Turn-Off Delay Time                               |                                                                           |     | 14   | 25   | ns    |

| t <sub>f</sub>                   | Turn-Off Fall Time                                |                                                                           |     | 9    | 17   | ns    |

| Qg                               | Total Gate Charge                                 | V <sub>DS</sub> = -15 V, I <sub>D</sub> = -4 A,                           |     | 10   | 14   | nC    |

| Q <sub>gs</sub>                  | Gate-Source Charge                                | V <sub>GS</sub> = -10 V                                                   |     | 2.2  |      | nC    |

| Q <sub>gd</sub>                  | Gate-Drain Charge                                 | 1                                                                         |     | 2    |      | nC    |

| Drain_S                          | ource Diode Characteristics                       | and Maximum Ratings                                                       |     | -    | -    | -     |

| ls                               | Maximum Continuous Drain–Source                   |                                                                           |     |      | -2.1 | Α     |

| V <sub>SD</sub>                  | Drain–Source Diode Forward<br>Voltage             | V <sub>GS</sub> = 0 V, I <sub>S</sub> = -2.1 A (Note 2)                   |     | -0.8 | -1.2 | V     |

#### Notes

R<sub>SUA</sub> is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins. R<sub>SUC</sub> is guaranteed by design while R<sub>SCA</sub> is determined by the user's board design.

50°C/W when mounted on a 1irr pad of 2 oz copper

b) 105°C/W when mounted on a .04 in² pad of 2 oz copper

c) 125°C/W when mounted on a minimum pad.

Scale 1:1 on letter size paper

2. Pulse Test: Pulse Width < 300 µs, Duty Cycle < 2.0%

#### **Typical Characteristics**

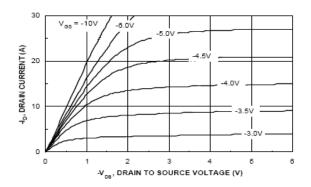

Figure 1. On-Region Characteristics.

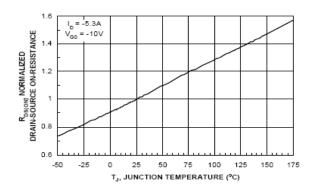

Figure 3. On-Resistance Variation with Temperature.

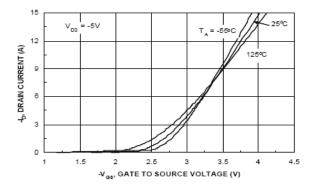

Figure 5. Transfer Characteristics.

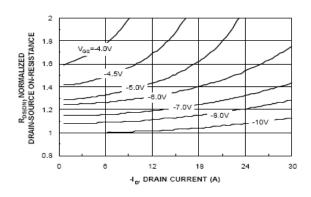

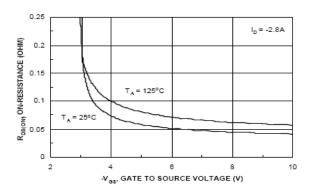

Figure 2. On-Resistance Variation with Drain Current and Gate Voltage.

Figure 4. On-Resistance Variation with Gate-to-Source Voltage.

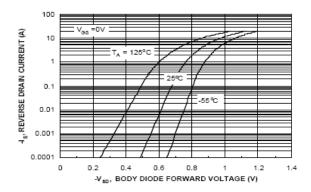

Figure 6. Body Diode Forward Voltage Variation with Source Current and Temperature.

#### **Typical Characteristics**

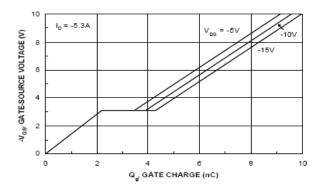

Figure 7. Gate Charge Characteristics.

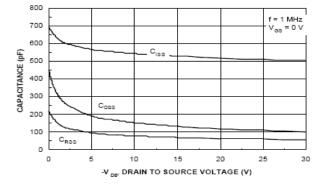

Figure 8. Capacitance Characteristics.

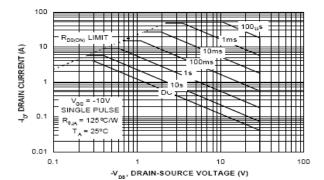

Figure 9. Maximum Safe Operating Area.

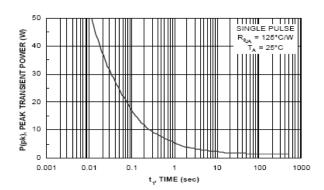

Figure 10. Single Pulse Maximum Power Dissipation.

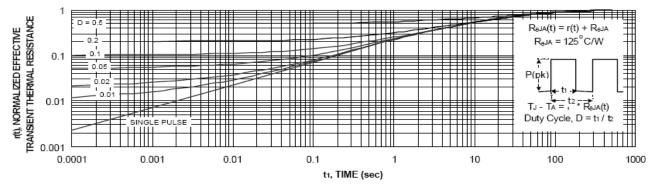

Figure 11. Transient Thermal Response Curve.

Thermal characterization performed using the conditions described in Note 1c. Transient thermal response will change depending on the circuit board design.

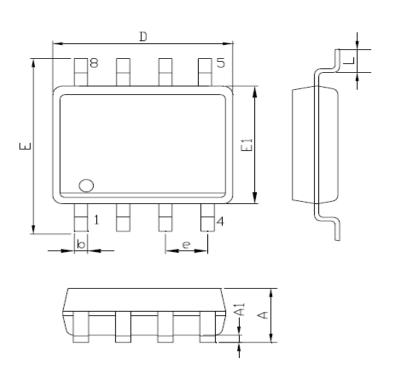

# **Packaging Information**

SOP-8

| SYMBOLS | MILLIMETERS |      | INCHES |       |  |

|---------|-------------|------|--------|-------|--|

| SIMBOLS | MIN.        | MAX. | MIN.   | MAX.  |  |

| A       | 1.35        | 1.75 | 0.053  | 0.069 |  |

| A1      | 0.10        | 0.25 | 0.004  | 0.010 |  |

| D       | 4.90        |      | 0.193  |       |  |

| Е       | 5.80        | 6.20 | 0.228  | 0.244 |  |

| E1      | 3.90        |      | 0.153  |       |  |

| L       | 0.40        | 1.27 | 0.016  | 0.050 |  |

| ь       | 0.31        | 0.51 | 0.012  | 0.020 |  |

| e       | 1.27        |      | 0.050  |       |  |